오늘은 최신 DRAM의 기술들에 대해 알아보도록 하겠습니다.

DRAM의 cell하나는 하나의 transistor와 하나의 capacitor로 구성되어 있습니다.

오늘은 capacitor를 어떻게 바꿀 수 있는지, transistor에서는 어떤 것을 바꿔서 dram cell 성능을 향상할 수 있는지 알아보겠습니다.

※ Capacitor

일단 capacitance를 구하는 식은 위의 그림과 같습니다. 우리는 parallel-plate를 생각하고 문제를 이해하면 됩니다.

그러면 저번 포스팅에서 설명했듯이 cell capacitance는 높일 수록 전하를 더 많이 저장할 수 있고, △Vth가 높아지게 되면서 sensing margin이 높아진다고 설명했습니다.

따라서 cell capacitance를 높이는 방법으로 기술이 개발되고 있습니다.

위 식에서 보면 Cell capacitance를 높이기 위해서 뭘 할 수 있을까요?

1. 유전상수가 큰 유전물질을 사용한다. (ε)

일단 유전상수가 큰 물질을 사용하게 된 이유가 뭘까요?

먼저 우리는 SiO2를 유전물질로 사용해왔습니다.

식에 의하면 d(두께)값을 낮추면 Capacitance를 높일 수 있습니다.

하지만 두께가 너무 얇아지는 경우 breakdown이 일어나게 되고, 신뢰성 문제가 생깁니다.

그래서 두께는 두껍게 하여 신뢰성 문제를 일으키지 않으면서 capacitance값을 높일 수 있도록 유전상수가 큰 물질(high-k dielectric)을 사용하는 것입니다.

(참고로 gate oxide에 들어가는 유전물질은 유전상수가 작은 물질을 사용합니다. - low-k dielectric)

하지만 무작정 유전상수(K)값이 큰 물질을 사용하면 되는 걸까요?

제가 위 그래프에서 보여드리려는 것은 유전상수 값이 클수록 Band Gap이 낮아진다는 것입니다.

이렇게 되면 전자가 에너지를 받아서 유연치않게 band gap을 뛰어 넘어가버리는 경우가 생깁니다..

이런 또다른 신뢰성 문제 때문에 엔지니어는 유전상수와 bandgap을 둘 다 고려하여 적절한 물질을 사용해야 합니다.

2. 길이를 길게 해서 단면적을 넓힌다. (A, 원기둥 모양을 생각하면 길이가 길어질수록 면적이 넓어집니다.)

이와 같이 capacitor의 길이와 너비(길이/너비)의 비를 Aspect Ratio라고 부릅니다.

면적을 넓히기 위해서 H가 길어짐에 따라 Aspect ratio가 증가하고 있는 trend입니다.

하지만 무작정 이렇게 높게 만들 수는 없겠죠?

공정상의 문제도 있고, 신뢰성도 생각해야 합니다.

(출처 : ResearchGate)

이와 같이 capacitor의 길이만 늘이는 것이 아니라 모양을 살짝씩 바꿔서 면적을 늘리는 기술도 사용되고 있습니다.

Stack capacitor Technology development

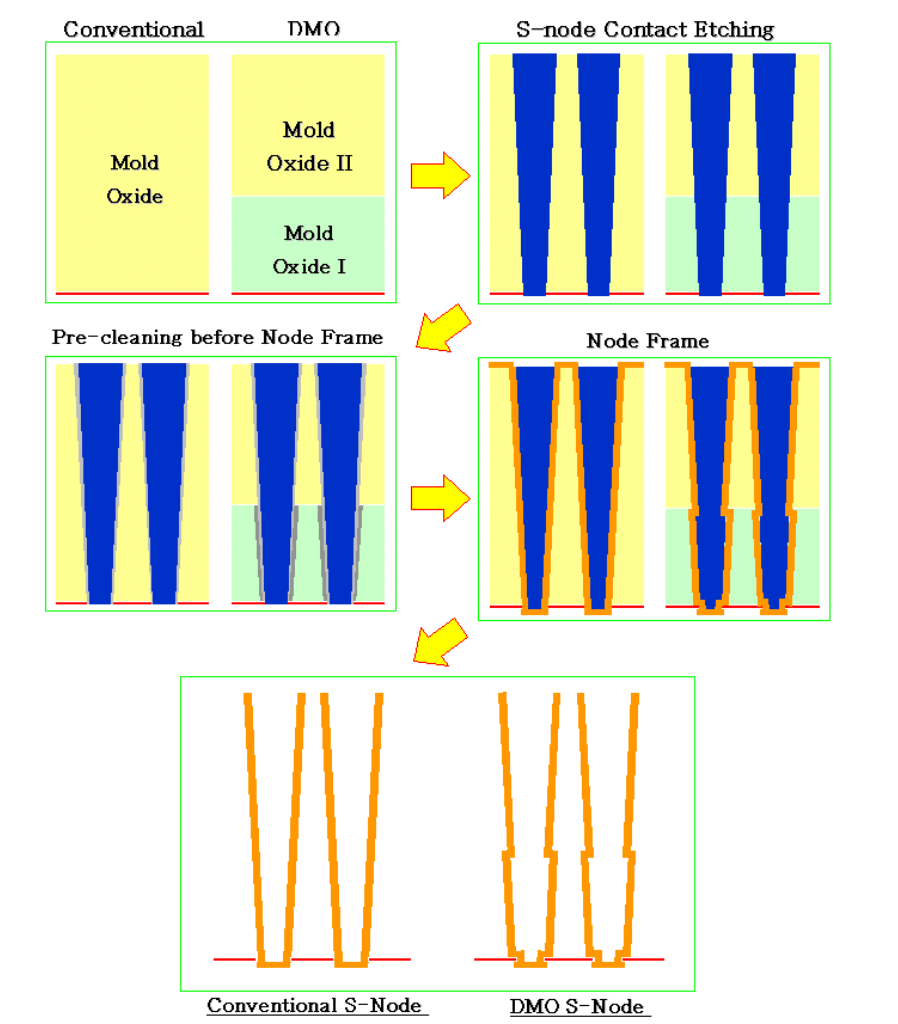

1. DMO, TMO(Double Mold Oxide, Triple Mold Oxide)

출처 : Journal of the Korean Physical Society, Vol. 41, No. 6, December 2002, pp. 884∼887

stack capacitor를 만들기 위해서는 etching을 깊게 해야합니다.

이때 한 번에 뚫게 되면 아래로 내려갈수록 좁아지는 모양이 됩니다.

따라서 DMO의 경우 왼쪽 그림과 같이 selectivity가 다른 두 물질을 이용하여 밑쪽의 etching 면적을 넓이는 것입니다.

아래의 mold oxide가 더 etching이 잘되는 물질이면, 밑으로 내려가도 구멍이 작아지지 않습니다.

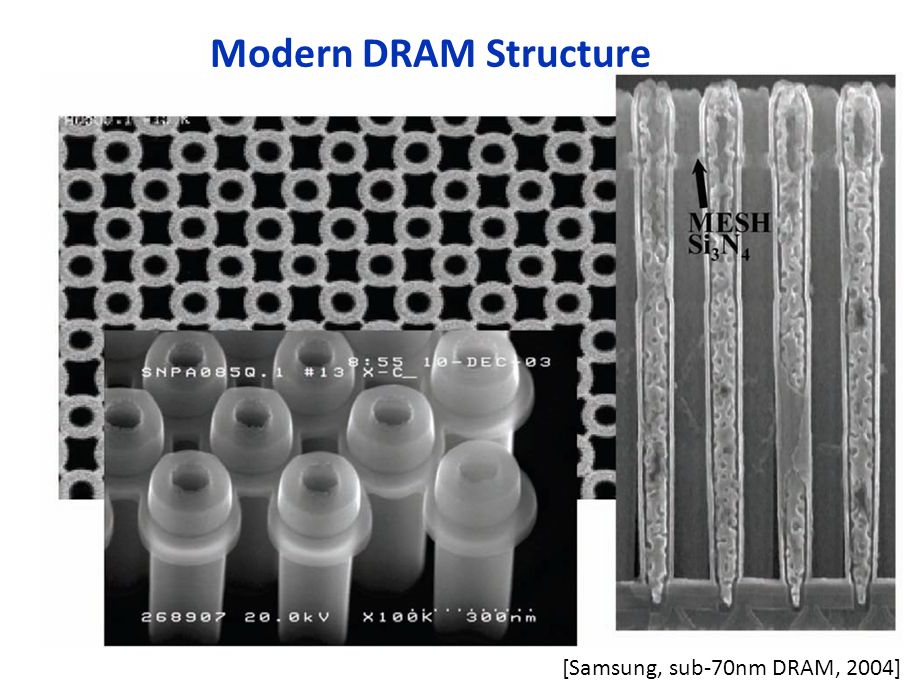

2. MESH

MESH는 Capacitor가 길면 중심을 잡지 못하고 쓰러질 수 있는데, 지지대 역할을 하는 것을 cap위쪽에 만들어주는 기술입니다.

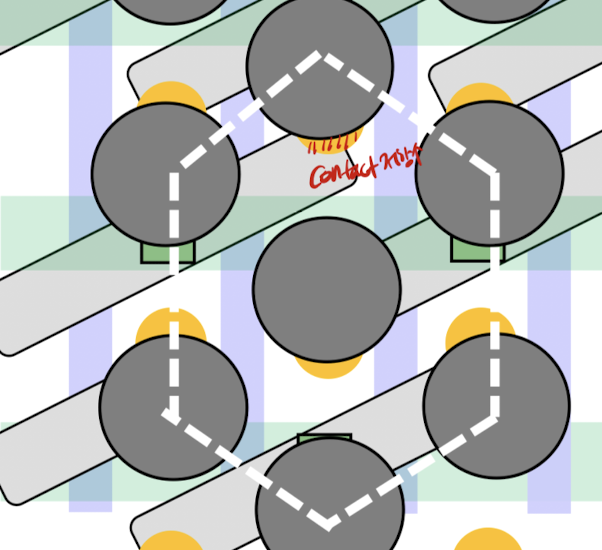

3. Honeycombo Structure

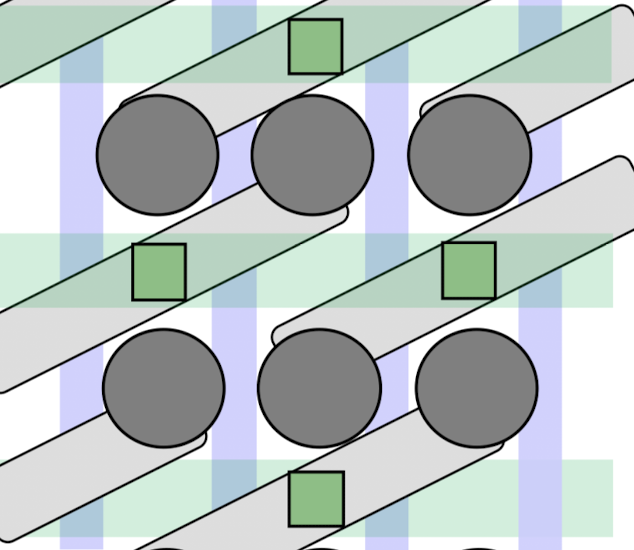

DRAM의 경우 6F2로 배열을 만들고 있습니다.

위에서 봤을 때 원래의 구조는 이렇게 되어 있었습니다.(capacitor가 회색 동그라미)

이렇게 벌집 모양을 만들면서 capacitor구멍 크기도 크게 만들고, density도 늘렸습니다.

오늘도 수고 많으셨습니다!!

좋은하루 되세요! 다 잘될겁니다 ㅎㅎ

'반도체 연구하기 > 메모리 반도체 소자' 카테고리의 다른 글

| 메모리 반도체 소자 - NAND FLASH, NOR FLASH 차이, 동작 원리 쉽게 이해하기! (0) | 2024.02.13 |

|---|---|

| DRAM cell 구조 쉽게 이해하기! 3D DRAM architecture, 8F2, 6F2, 4F2 (2) | 2024.02.09 |

| DRAM cell transistor 구조, RCAT, BCAT, SRCAT, DRAM architecture, 소자 구조 쉽게 이해하기 (2) | 2024.02.08 |

| Transistor leakage current, GIDL, DIBL(Vt roll-off, short channel effect) 핵심만! 쉽게 이해하기! (0) | 2024.02.08 |

| Transistor cell의 scaling challenges - 전압 측면 (0) | 2024.02.06 |

댓글