안녕하세요!

오늘은 Deposition, 증착 공정에 대해 포스팅하려고 합니다.

Deposition 종류가 너무도 많다보니

아마 이 part는 3개의 posting이 될 것 같습니다..

그래도 이왕 하는 거면 제대로 공부해야죠!

그래서 시작은 가볍게!

1. What is Deposition?

반도체 공정에서는 'Thin Film Deposition'이라고 불립니다.

얇은 박막을 형성하기 때문이죠.

이 공정은 왜 쓰냐?..

(복잡한 회로일수록 층수는 높아집니다.)

위 그림의 맨 위에서 Power, Signal 등의 전류 신호가 들어옵니다.

이 전류가 Transistor까지 전달되려면 금속 통로가 필요하겠죠?

따라서 각각의 층을 만들 때 Litho, Etch, Deposition 과정을 거치면서 금속, 유전체 층을 만들어갑니다.

이때 Deposition 공정을 사용하는 것이죠!

2. Requirements for TF Deposition

그러면 Thin Film Deposition 공정을 진행할 때 고려해야 할 변수들을 살펴보겠습니다.

1) Composition

증착할 물질의 구성이 맞는지 확인해야 합니다.

이를 Stoichiometry(화학변량)이라고 부릅니다.

금속인 경우 단일 원소로 이루어져 있기 때문에 Alloy(합금)을 만들지 않는 한 따지지 않아도 되지만,

유전체를 증착할 때는 중요한 요소가 됩니다.

예를 들면 이런 식으로 Copper와 Oxygen의 비율을 고려해야 합니다.

2) Thickness Uniformity

증착은 웨이퍼 전면에서 이루어지기 때문에 모든 면들이 동일한 두께로 증착되어야 합니다.

그래야 다음 공정인 Litho가 이루어질 때 오류가 나지 않습니다.

그래서 보통은 CMP 공정을 추가적으로 진행합니다.

이를 측정할 때는

Within wafer(웨이퍼 한 개 내에서 두께가 동일한지)-WIW

Wafer to Wafer(각각의 웨이퍼 두께가 동일한지)-WTW

Lot to Lot(25개의 wafer가 담긴 box와 다른 box의 두께 동일한지)-LTL

등을 고려합니다.

3) Step Coverage(=Conformal Coverage)

쉽게 말하면 증착한 위, 아래, 옆면이 같은 두께로 되었는지를 판단하는 변수입니다.

Conformal 하다 = Step coverage가 좋다

다음과 같은 그림이 있을 때

T=S=B 인 상황이 Conformal 한 상황입니다.

보통은 S/T 를 보고 판단합니다.

왜냐하면 T는 박막이 가장 잘 형성되는 부분이고

S는 가장 잘 형성되지 않는 부분이기 때문입니다.

(이를 Conformality와 비교하기도 하는데, 이 부분은 넘어가겠습니다.)

4) Gap Filling

증착 공정을 진행할 때 가장 피해야 하는 것이 Gap입니다.

즉 증착을 했는데 가운데 void가 생기는 것이죠.

이러면 그냥 Fail입니다!!!

위 그림과 같이 (c)가 완벽한 상황이고,

(a)&(b)는 void가 발생한 경우입니다..

이때 (b)는 conformal 하게 보이는데 왜 void가 있을까? 궁금할 수 있습니다.

이는 다음 posting의 CVD 할 때 다루겠습니다.

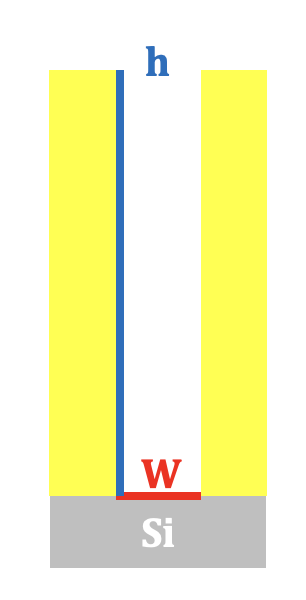

Gap Filling과 관련해서 AR(Aspect Ratio)를 알아야 합니다.

이는 높이를 너비로 나눈 값입니다.(h/w)

AR이 클수록 gap filling이 어려워집니다.

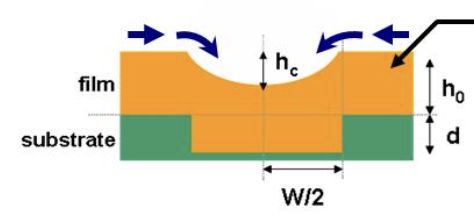

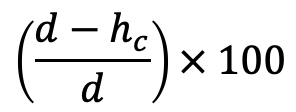

5) Planarization

다음과 같이 Deposition 했을 때,

DOP(Degree of Planarization) %

마지막으로

PVD(Physical Vapor Deposition)

CVD(Chemical Vapor Deposition)

이 두 가지가 언제 쓰이는지 보겠습니다.

이를 다룬 글이 별로 없어서...!

| Types | CVD | PVD |

| 반응 온도 | 고온(600-1000도) | 저온(450-500도) |

| 증착 원리 | 가스의 전리 반응 | 물리적으로 박막 조성 |

| 하부막 접착력 | 우수 | 상대적 취약 |

| 증착 두께 | 두꺼운 막 조성 가능 | CVD 대비 얇은 막 |

| Step coverage | 우수 | CVD 대비 취약 |

| 가격 | 보통 | 높음(순도 높은 금속물질을 사용하기 때문) |

| 공정 분류 | APCVD, LPCVD, PECVD etc. | Sputtering, Evaporation etc. |

PVD

1. 금속을 증착할 경우 사용

이유 : 금속은 열에 예민한데 PVD는 낮은 온도를 사용

2. 고순도 물질을 증착할 경우 사용

이유 : chamber 내의 압력이 CVD보다 훨씬 낮기 때문에

그만큼 불순물도 적음

CVD

1. 유전체를 증착할 경우 사용

이유 : 화합물이기 때문에 화학반응으로 증착하는 것이 유리

2. 두꺼운 박막 만들 때 사용

이유 : 빠르게 증착되기 때문

3. Step coverage가 좋아야 하는 경우, 복잡한 구조체의 경우 사용

이유 : 온도가 높아서 고르게 박막이 조성되고, PVD는 직선으로 움직이기 때문에 step coverage가 좋지 않음.

오늘도 수고하셨습니다!

여러분 꼭 행복하세요 :)

건강이 우선입니다!

댓글